#### **Public Products List**

Publict Products are off the shelf products. They are not dedicated to specific customers, they are available through ST Sales team, or Distributors, and visible on ST.com

PCN Title: VIPower Products (SO-8): Assembly and Final Test Transfer to Bouskoura (second wave)

PCN Reference: ADG/23/13915

Subject: Public Products List

Dear Customer,

Please find below the Standard Public Products List impacted by the change.

| VN800PSTR-E | VN750SMPTR-E | VN750PSTR-E |

|-------------|--------------|-------------|

|-------------|--------------|-------------|

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

Subject to any contractual arrangement in force with you or to any industry standard implemented by us, STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics - All rights reserved

## PRODUCT/PROCESS CHANGE NOTIFICATION

| TITLE          | VIPower Products (SO-8): Assembly and Final Test Transfer to Bouskoura fgYWcbX'k Uj YŁ            |

|----------------|---------------------------------------------------------------------------------------------------|

| IMPACTED       | VIPower products housed in SO-8 package.                                                          |

| PRODUCTS       | See enclosed list.                                                                                |

| MANUFACT. STEP | Assembly and Final Testing                                                                        |

| INVOLVED PLANT | Recipient: ST Shenzhen Plant (China)                                                              |

|                | Destination: ST Bouskoura Plant (Morocco)                                                         |

| CHANGE REASON  | ST Shenzhen SO8 package line closure June 30, 2023:                                               |

|                | Service and Capacity improvement for business continuity.                                         |

|                | Manufacturing process optimization.                                                               |

| CHANGE         | Transfer of package assembly and Final testing from current Shenzhen                              |

| DESCRIPTION    | (China) to Bouskoura (Morocco) Plant. Package Bill of Material is subject                         |

| _              | to upgrade as described in the following document.                                                |

| TRACEABILITY   | Dedicated Finished Good code (internal part number).                                              |

| VALIDATION     | According to ZVEI Delta Qualification Matrix corresponding to following selected items:           |

|                | SEM-PA-04 Change of lead frame finishing material / area (internal)                               |

|                | ♣ SEM-PA-05 Change of lead and slug plating material /plating tickness (external)                 |

|                | ♣ SEM-PA-18 Move all or parts of production to a different assembly site  • site                  |

|                | SEM-TF-01 Move of all or part of electrical wafer test and/or final test to a different test site |

|                | See following document for details and attached qualification report.                             |

| CURRENT        | Replaced by new version featuring new Plant and upgraded package                                  |

| REPORTS"       | Qualification performed on Test Vehicles enclosed to this communication                           |

VIPower® products in SO-8 package: Assembly and Final Test Transfer to Bouskoura (second wave)

## Agenda

3 Change Description

9 Product lines impacted

5 Lead Frame Options

- 10 Conclusions

- 7 Bill Of Material Comparison

- 8 ZVEI Guidelines

## Change description

- Aim of this document is to describe the activity performed to qualify the VIPower® products assembled in SO-8 package with the **S**uper**S**uper**H**igh**D**ensity Lead Frame in Bouskoura ST plant.

- The new Lead Frame material **S**uper**S**uper**H**igh**D**ensity ensure the same quality and electrical characteristics the current products processed in Shenzhen ST plant with the **H**igh**D**ensity Lead Frame.

- All reliability tests have been completed with positive results.

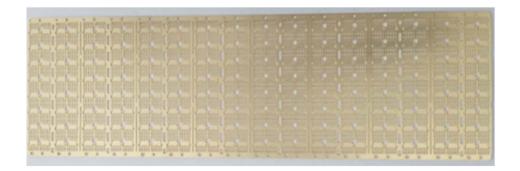

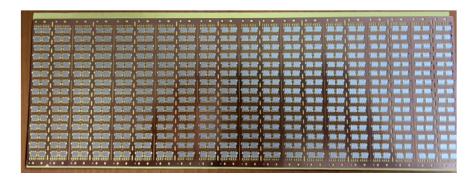

# SO8 Lead Frame Density comparison: High Density vs Super Super High Density

• **256** Units (8 rows, 32 columns) for each Leed Frame **H**igh **D**ensity in Shenzhen plant

600 Units (15 rows, 40 columns) for each Leed Frame Super Super High Density in Bouskoura ST plant.

## SO8 SSHD Lead Frame option

## SO8 Lead Frame Option

| Leadframe PN                 | FRAME SO 8L 92x169 6+2<br>SSHD 600uOpK SpAg |

|------------------------------|---------------------------------------------|

| <b>H</b> igh <b>D</b> ensity | OPT K                                       |

| in Shenzhen ST plant         | PPF                                         |

| Super Super High Density     | OPT K                                       |

| in Bouskoura ST plant        | Spag                                        |

## FRAME SO 8L 92x169 6+2 SSHD 600uOpK SpAg

## **Bill Of Material Comparison**

## SO 08 STRIP SINGLE ISLAND package

| Actual Bill of Material in SHENZHEN plant |                                       |  |  |  |  |  |  |  |

|-------------------------------------------|---------------------------------------|--|--|--|--|--|--|--|

| ITEM                                      | MATERIAL                              |  |  |  |  |  |  |  |

| WIRE                                      | WIRE Cu D2 BL40-55g EL15-25%          |  |  |  |  |  |  |  |

| FRAME                                     | SO 8L 169x92 Mtx HD OpK<br>NiThPdAgAu |  |  |  |  |  |  |  |

| DIE ATTACH                                | GLUE LOCTITE ABLESTIK<br>QMI95072A1   |  |  |  |  |  |  |  |

| MOLD COMPOUND                             | RESIN SUMITOMO EME-G700KC             |  |  |  |  |  |  |  |

| Actual Bill of Material in BOUSKOURA plant |                                       |  |  |  |  |  |  |

|--------------------------------------------|---------------------------------------|--|--|--|--|--|--|

| ITEM                                       | MATERIAL                              |  |  |  |  |  |  |

| WIRE                                       | WIRE Cu D2 BL40-55g EL15-25%          |  |  |  |  |  |  |

| FRAME                                      | SO 8L 92x169 6+2 SSHD 600uOpK<br>SpAg |  |  |  |  |  |  |

| DIE ATTACH                                 | GLUE LOCTITE ABLESTIK<br>QMI95072A1   |  |  |  |  |  |  |

| MOLD COMPOUND                              | RESIN SUMITOMO EME-G700KC             |  |  |  |  |  |  |

## **ZVEI** Guidelines

• According to ZVEI recommendations, the notification is required.

|           | Assessment of impact on Supply Chain regarding following aspects - contractual agreements - technical interface of processability/manufacturability of customer - form, fit, function, quality performance, reliability | Remaining risks within Supply Chain? |     | risks within<br>Supply                                                                                                                  |                                                                                                                                     | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | risks within<br>Supply |  | Understanding of semiconductors<br>experts | Examples to explain |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|--------------------------------------------|---------------------|

| ID        | Type of change                                                                                                                                                                                                          | No                                   | Yes |                                                                                                                                         |                                                                                                                                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

| ,         | ANY                                                                                                                                                                                                                     |                                      |     |                                                                                                                                         |                                                                                                                                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

|           | DATA SHEET                                                                                                                                                                                                              |                                      |     |                                                                                                                                         |                                                                                                                                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

|           | DESIGN                                                                                                                                                                                                                  |                                      |     |                                                                                                                                         |                                                                                                                                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

|           | PROCESS - WAFER PRODUCTION                                                                                                                                                                                              |                                      |     |                                                                                                                                         |                                                                                                                                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

|           | BARE DIE                                                                                                                                                                                                                |                                      |     |                                                                                                                                         |                                                                                                                                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

|           | PROCESS - ASSEMBLY                                                                                                                                                                                                      |                                      |     |                                                                                                                                         |                                                                                                                                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

| SEM-PA-04 | Change of lead frame finishing material / area (internal)                                                                                                                                                               | Р                                    | Р   | Change of surface material of die attach pad and second bond area (e.g. influence in adhesion to mold compound, wedge bond reliability) | e. g. change from Ag flash to NiP protection layer<br>e. g. change from Ag spot to Au spot<br>e. g. increase of silver plating area |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

| SEM-PA-05 | Change of lead and heat slug plating material/plating thickness (external)                                                                                                                                              | Р                                    | Р   | Change in material and / or process resulting in a new technology (e.g. pure tin).                                                      | e.g. change in heat slug stack<br>e.g. change from Sn into Ni/Pd/Au<br>e.g. change of layer thickness                               |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

| SEM-PA-18 | Move all or parts of production to a different assembly site.                                                                                                                                                           | Ф                                    | Р   | Assembly transfer or relocation. Includes transfer as well as additional site.                                                          | e.g. dual source / fab strategy                                                                                                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

|           | PACKING/SHIPPING                                                                                                                                                                                                        |                                      |     |                                                                                                                                         |                                                                                                                                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

|           | EQUIPMENT                                                                                                                                                                                                               |                                      |     |                                                                                                                                         |                                                                                                                                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

|           | TEST FLOW                                                                                                                                                                                                               |                                      |     |                                                                                                                                         |                                                                                                                                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

| SEM-TF-01 | Move of all or part of electrical wafer test and/or final test to a different test site.                                                                                                                                | Р                                    | Р   | Tester transfer or relocation. Check impact on SEM-AN-01 Includes transfer as well as additional site.                                  | Dual source strategy                                                                                                                |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                                            |                     |

## VIPower® Product lines impacted

#### VIPower® Product lines in SO 08 STRIP SINGLE ISLAND package

• Commercial Product : VN800PSTR-E (Silicon Line VNT903)

VN800PSTR-61-E (Silicon Line VNT903)

Commercial Product : VN750SMPTR-E (Silicon Line VNE801)

• Commercial Product : VN750PSTR-E (Silicon Line VNE701)

## Conclusions

- Detailed qualification activity has been performed in order to qualify the VIPower® products assembled in SO-8 package with the SuperSuperHighDensity Lead Frame in Bouskoura ST plant.

- All reliability tests have been completed with positive results;

- This report shows the positive results achieved processing the VIPower® products assembled in SO-8 package and the SuperSuperHighDensity Lead Frame, ensuring the same quality and electrical characteristics as the current production in Shenzhen ST plant.

## **Reliability Evaluation Report**

VIPower® MO3, MO5, M07 Technologies SO8 – ST Bouskoura (Morocco) Assembly plant

**Note:** this report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the electronic device conformance to its specific mission profile for Automotive Application. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics or under the approval of the author (see below).

#### **Revision history**

| Rev. | Changes description          | Author     | Date       |

|------|------------------------------|------------|------------|

| 1    | Full AEC-Q100 plan completed | A. Vilardo | 12/12/2022 |

#### Approved by

| Function                     | Location           | Name       | Date       |

|------------------------------|--------------------|------------|------------|

| Division Reliability Manager | ST Catania (Italy) | A. Marmoni | 12/12/2022 |

RERLVIP22035 Page 1 of 20

## **TABLE OF CONTENTS**

| 1 | RELIABILIT | Y EVALUATION OVERVIEW           | 3  |

|---|------------|---------------------------------|----|

|   | 1.1 OBJEC  | TIVE                            | 3  |

|   |            | BILITY STRATEGY AND TEST PLAN   |    |

|   | 1.2.1      | Reliability strategy            | 3  |

|   | 1.2.2      | Test Plan                       |    |

|   | 1.3 CONC   | LUSION                          | 5  |

| 2 | PRODUCT (  | CHARACTERISTICS                 | 6  |

|   | 2.1 GENER  | RALITIES                        | 6  |

|   | 2.2 PINS C | CONNECTION                      | 11 |

|   | 2.3 BLOCK  | C DIAGRAM                       | 12 |

|   | 2.4 BOND   | ING DIAGRAM                     | 13 |

|   | 2.5 TRACE  | EABILITY                        | 14 |

|   | 2.5.1      | Wafer Fab information           | 14 |

|   | 2.5.2      | Assembly information            | 14 |

|   | 2.5.3      | Reliability testing information | 14 |

| 3 | TESTS RESU | JLTS SUMMARY                    | 15 |

|   | 3.1 Lots   | Information                     | 15 |

|   | 3.2 TEST I | RESULTS SUMMARY                 | 16 |

|   |            |                                 |    |

|   |            |                                 |    |

|   |            |                                 |    |

#### 1 RELIABILITY EVALUATION OVERVIEW

### 1.1 Objective

Aim of this report is to present the results of the reliability evaluation performed on selected test vehicles involving the VIPower®M03, MO5 and MO7 Technologies assembled in package SO8 with the new Super Super High Density (SSHD) lead frame in ST Bouskoura (Morocco) assembly plant.

The selected vehicles are:

- VIPower®M03 Technology:

- VNS3NV04DP-E (VNS6 as ST internal code)

- VNS14NV04P-E (VNT8 as ST internal code)

- VIPower®M05 technology:

- o VN5160S-E (VNJ5 as ST internal code)

- VNLD5090E (VNY9 as ST internal code)

- VIPower®M07 technology:

- VN7040AS (XV14 as ST internal code)

## 1.2 Reliability Strategy and Test Plan

#### 1.2.1 Reliability strategy

The reliability strategy was based on one diffusion lot per each test vehicles, involving different Wafer Fab locations, assembly each lot in the nominal (NN) Bonding Force and US Power condition as well as in the higher (HH) and lower (LL) case for a total amount of fifteen assembly lots.

The reliability evaluation is in agreement with ST 0061692 and AEC-Q100 rev. H Grade 1 requirements. For details on test conditions, generic data used, and specifications references refer to test results summary in section 3.

In the below table a comparison among AEC-Q100 and ZVEI requirements in case of assembly plant transfer and new frame introduction vs the applied ST plan is reported, no deviation occurred.

|          |     | Tes | t Gro | up A |      | Te<br>Grou |      | Т   | est G | roup | С  | Test Group D |      |     | Test Group E |    |     |     |    |    |     |    |

|----------|-----|-----|-------|------|------|------------|------|-----|-------|------|----|--------------|------|-----|--------------|----|-----|-----|----|----|-----|----|

|          | ТНВ | AC  | тс    | РТС  | HTSL | HTOL       | ELFR | WBS | WBP   | SD   | PD | EM           | TDDB | нсі | NBTI         | SM | нвм | СДМ | LU | ED | ЕМС | SC |

| AEC-Q100 | х   | х   | х     | х    | х    | х          | х    | х   | х     | х    | х  |              |      |     |              |    |     |     |    | х  |     |    |

| ZVEI     | х   | х   | х     | х    | х    | х          | х    | х   | х     | х    | х  |              |      |     |              |    |     |     |    | х  |     |    |

| ST       | х   | Х   | х     | х    | х    | х          | х    | х   | х     | х    | х  |              |      |     |              |    |     |     |    | х  |     |    |

RERLVIP22035 Page 3 of 20

## 1.2.2 Test Plan

## AEC-Q100 TEST PLAN

| TEST GROUP                                       | TEST NAME                          | DESCRIPTION / COMMENTS                               | TEST FLAG      |

|--------------------------------------------------|------------------------------------|------------------------------------------------------|----------------|

| A                                                | PC (JL3)                           | Preconditioning (JL3+3 reflows simulation)           | Yes            |

| Accelerated                                      | ТНВ                                | Temperature Humidity Bias                            | Yes            |

| Environment Stress                               | AC                                 | Autoclave at 2atm                                    | Yes            |

| Tests                                            | тс                                 | Temperature Cycling                                  | Yes            |

|                                                  | PTC                                | Power Temperature Cycling                            | Yes            |

|                                                  | HTSL                               | High Temperature Storage Life                        | Yes            |

| В                                                | HTOL                               | High Temperature Operating Life                      | Yes            |

| Accelerated Lifetime                             | ELFR                               | Early Life Failure Rate                              | Yes            |

| Simulation Tests                                 | EDR                                | Endurance Data Retention                             | Not Applicable |

| С                                                | WBS                                | Wire Bond Shear                                      | Yes            |

| Package Assembly                                 | WBP                                | Wire Bond Pull                                       | Yes            |

| Integrity Tests                                  | SD                                 | Solderability                                        | Yes            |

|                                                  | PD                                 | Physical Dimension                                   | Yes            |

|                                                  | SBS                                | Solder Ball Shear                                    | Not Applicable |

|                                                  | LI                                 | Lead Integrity                                       | Not Applicable |

| <b>D</b><br>Die Fabrication<br>Reliability Tests | Test list is reported in section 5 | Performed during process qualification               | Not Applicable |

| E                                                | ESD (HBM)                          | Electrostatic Discharge (Human Body Model)           | Not Applicable |

| Electrical Verification                          | ESD (CDM)                          | Electrostatic Discharge (Charged Device Model)       | Not Applicable |

| Tests                                            | LU                                 | Latch Up                                             | Not Applicable |

|                                                  | ED                                 | Electrical distribution                              | Yes            |

|                                                  | FG                                 | Fault grading                                        | Not Applicable |

|                                                  | CHAR                               | Characterization                                     | Not Applicable |

|                                                  | EMC                                | Electromagnetic Compatibility                        | Not Applicable |

|                                                  | SC                                 | Short Circuit Characterization                       | Not Applicable |

|                                                  | SER                                | Soft Error Rate                                      | Not Applicable |

|                                                  | LF                                 | Lead (Pb) Free: (see AEC-Q005)                       | Not Applicable |

| <b>F</b> Defect Screening Tests                  | Test list is reported in section 5 | To be implemented starting from first production lot | No             |

| <b>G</b><br>Cavity Package<br>Integrity Tests    | Test list is reported in section 5 | N/A: not for plastic packaged devices                | Not Applicable |

RERLVIP22035 Page 4 of 20

#### 1.3 Conclusion

Reliability tests have been completed with positive results. Neither functional nor parametric rejects were detected at final electrical testing.

Relevant Destructive Physical Analysis (DPA) performed by means Wire Bond Pull/Shear tests (WBP, WBS) performed on each assembly lots (=assembly configuration) after the package oriented stress test pointed out neither abnormal break loads nor forbidden failure modes. The delamination check performed by means Scanning Acoustic Microscopy (SAM) analysis shows no significant delamination through the die-attach layer and its interfaces, nor on die-pad.

Based on the overall results obtained, the selected test vehicles designed in VIPower®M03, M05 and M07 technologies and assembled on SO8 package with the new SSHD frame in ST Bouskoura (Morocco) assembly plant, has positively passed reliability evaluation performed in agreement to AEC\_Q100 Rev. H Grade 1 specification.

RERLVIP22035 Page **5** of **20**

#### 2. Product Characteristics

#### 2.1. Generalities

## VNS3NV04DP-E

**OMNIFET II**

fully autoprotected Power MOSFET

#### **Features**

| Max on-state resistance (per ch.) | R <sub>ON</sub> | $120\text{m}\Omega$ |

|-----------------------------------|-----------------|---------------------|

| Current limitation (typ)          | LIMH            | 3.5 A               |

| Drain-source clamp voltage        | VCLAMP          | 40 V                |

- ECOPACK®: lead free and RoHS compliant

- Automotive Grade: compliance with AEC guidelines

- Linear current limitation

- Thermal shutdown

- Short circuit protection

- Integrated clamp

- Low current drawn from input pin

- Diagnostic feedback through input pin

- ESD protection

- Direct access to the gate of the Power MOSFET (analog driving)

- Compatible with standard Power MOSFET

#### Description

The VNS3NV04DP-E device is made up of two monolithic chips (OMNIFET II) housed in a standard SO-8 package. The OMNIFET II is designed using STMicroelectronics™ VIPower™ M0-3 technology and is intended for replacement of standard Power MOSFETs in up to 50 kHz DC applications.

Built-in thermal shutdown, linear current limitation and overvoltage clamp protect the chip in harsh environments.

Fault feedback can be detected by monitoring voltage at the input pin

Table 1. Device summary

|  | Package | Order codes  |                |

|--|---------|--------------|----------------|

|  | Package | Tube         | Tape and reel  |

|  | SO-8    | VNS3NV04DP-E | VNS3NV04DPTR-E |

RERLVIP22035 Page **6** of **20**

## VNS14NV04P-E

"OMNIFET II" fully autoprotected Power MOSFET

#### Features

| Туре         | R <sub>DS(on)</sub> | I <sub>IIm</sub> | V <sub>clamp</sub> |

|--------------|---------------------|------------------|--------------------|

| VNS14NV04P-E | 35 mΩ               | 12 A             | 40 V               |

- Linear current limitation

- Thermal shutdown

- Short circuit protection

- Integrated clamp

- Low current drawn from input pin

- Diagnostic feedback through input pin

- ESD protection

- Direct access to the gate of the Power MOSFET (analog driving)

- Compatible with standard Power MOSFET

## Description

The VNS14NV04P-E is monolithic device made using STMicroelectronics™ VIPower™ M0

Technology, intended for replacement of standard Power MOSFETs in DC to 50 KHz applications.

Built-in thermal shutdown, linear current limitation and overvoltage clamp protect the chip in harsh environments.

Fault feedback can be detected by monitoring the voltage at the input pin.

Table 1. Device summary

| Pankann | Order codes  Tube Tape and reel |                |  |

|---------|---------------------------------|----------------|--|

| Package | Tube                            | Tape and reel  |  |

| SO-8    | VNS14NV04P-E                    | VNS14NV04PTR-E |  |

RERLVIP22035 Page **7** of **20**

## VN5160S-E

## Single channel high side driver for automotive applications

#### Features

| Max supply voltage                | V <sub>CC</sub>   | 41V                 |

|-----------------------------------|-------------------|---------------------|

| Operating voltage range           | V <sub>CC</sub>   | 4.5 to 36V          |

| Max on-state resistance (per ch.) | R <sub>ON</sub>   | 160 mΩ              |

| Current limitation (typ)          | I <sub>LIMH</sub> | 5.4 A               |

| Off-state supply current          | Is                | 2 μA <sup>(1)</sup> |

1. Typical value with all loads connected

#### Main

- Inrush current active management by power limitation

- Very low stand-by current

- 3.0V CMOS compatible input

- Optimized electromagnetic emission

- Very low electromagnetic susceptibility

- In compliance with the 2002/95/EC european directive

#### Diagnostic Functions

- Open drain status output

- On-state open load detection

- Off-state open load detection

- Thermal shutdown indication

#### Protection

- Undervoltage shutdown

- Overvoltage clamp

- Output stuck to Vcc detection

- Load current limitation

- Self limiting of fast thermal transients

- Protection against loss of ground and loss of V<sub>CC</sub>

- Thermal shutdown

#### Table 1. Device summary

- Reverse battery protection (see Figure 28)

- Electrostatic discharge protection

#### Applications

All types of resistive, inductive and capacitive loads

### Description

The VN5160S-E is a monolithic device made using STMicroelectronics VIPower M0-5 technology. It is intended for driving resistive or inductive loads with one side connected to ground. Active V<sub>CC</sub> voltage clamp protects the device against low energy spikes. The device detects open load condition both in on and offstate, when STAT\_DIS is left open or driven low. Output shorted to V<sub>CC</sub> is detected in the off-state. When STAT DIS is driven high, STATUS is in a high impedance condition. Output current limitation protects the device in overload condition. In case of long duration overload, the device limits the dissipated power to safe level up to thermal shutdown intervention. Thermal shutdown with automatic restart allows the device to recover normal operation as soon as fault condition disappears.

| Package  | Order codes |               |  |  |

|----------|-------------|---------------|--|--|

| 1 ackage | Tube        | Tape and reel |  |  |

| SO-8     | VN5160S-E   | VN5160STR-E   |  |  |

RERLVIP22035 Page 8 of 20

## VNLD5090-E

## OMNIFET III fully protected low-side driver for automotive applications

Datasheet - production data

#### **Features**

| Туре       | V <sub>clamp</sub> | R <sub>DS(on)</sub> | ID   |

|------------|--------------------|---------------------|------|

| VNLD5090-E | 41 V               | 90 mΩ               | 25 A |

AEC-Q100 qualified

- Drain current: 13 A

- ESD protection

- Overvoltage clamp

- Thermal shutdown

- Current and power limitation

- Very low standby current

- Very low electromagnetic susceptibility

- In compliance with the 2002/95/EC European directive

## Description

The VNLD5090-E is a monolithic device made using STMicroelectronics VIPower technology, intended for driving resistive or inductive loads with one side connected to the battery. Built-in thermal shutdown protects the chip from overtemperature and short-circuit. Output current limitation protects the device in an overload condition. In case of long duration overload, the device limits the dissipated power to a safe level up to thermal shutdown intervention. Thermal shutdown, with automatic restart, allows the device to recover normal operation as soon as a fault condition disappears. Fast demagnetization of inductive loads is achieved at turn-off.

Table 1. Device summary

| Package | Order codes       |              |  |

|---------|-------------------|--------------|--|

| Package | Tube Tape and ree |              |  |

| SO-8    | VNLD5090-E        | VNLD5090TR-E |  |

RERLVIP22035 Page **9** of **20**

#### VN7040AJ, VN7040AS

Datasheet

#### High-side driver with MultiSense analog feedback for automotive applications

Product status link

VN7040AJ

VN7040AS

#### **Features**

| Max transient supply voltage      | Vcc               | 40 V      |

|-----------------------------------|-------------------|-----------|

| Operating voltage range           | V <sub>cc</sub>   | 4 to 28 V |

| Typ. on-state resistance (per Ch) | R <sub>ON</sub>   | 40 mΩ     |

| Current limitation (typ)          | I <sub>LIMH</sub> | 34 A      |

| Standby current (max)             | I <sub>STBY</sub> | 0.5 μΑ    |

- General

- Single channel smart high-side driver with MultiSense analog feedback

- Very low standby current

- Compatible with 3 V and 5 V CMOS outputs

- MultiSense diagnostic functions

- Multiplexed analog feedback of: load current with high precision proportional current mirror, V<sub>CC</sub> supply voltage and T<sub>CHIP</sub> device temperature

- Overload and short to ground (power limitation) indication

- Thermal shutdown indication

- OFF-state open-load detection

- Output short to V<sub>CC</sub> detection

- Sense enable/disable

- Protections

- Undervoltage shutdown

- Overvoltage clamp

- Load current limitation

- Self limiting of fast thermal transients

- Configurable latch-off on overtemperature or power limitation with dedicated fault reset pin

- Loss of ground and loss of V<sub>CC</sub>

- Reverse battery with external components

- Electrostatic discharge protection

#### Applications

- All types of Automotive resistive, inductive and capacitive loads

- Specially intended for Automotive Turn Indicators (up to P27W or SAE1156 and R5W paralleled or LED Rear Combinations)

- Protected supply for ADAS systems: radars and sensors

RERLVIP22035 Page 10 of 20

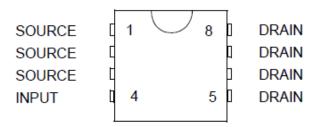

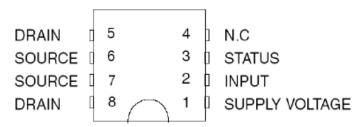

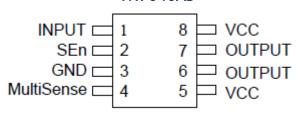

#### 2.2. pins connection

#### VNS3NV04DP-E, VNS14NV04P-E

#### VN5160S-E

#### VNLD5090-E

#### **VN7040AS**

RERLVIP22035 Page 11 of 20

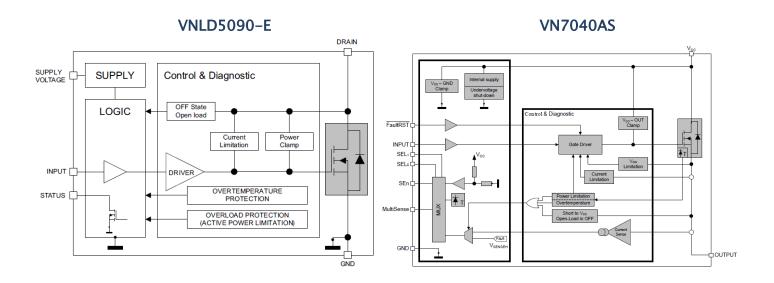

## 2.3. Block diagrams

#### VNS3NV04DP-E, VNS14NV04P-E VN5160S-E V<sub>CC</sub> DRAIN Overvoltage V<sub>CC</sub> CLAMP UNDERVOLTAGE Clamp GND INPUT INPUT LOGIC STATUS OPENLOAD ON STAT\_DIS Over Temperature Pwr<sub>LIM</sub> SOURCE

RERLVIP22035 Page **12** of **20**

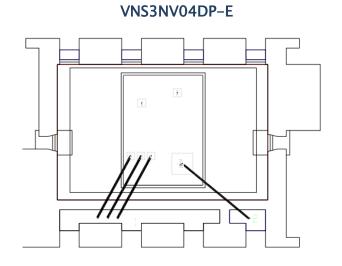

## 2.4. Bonding diagrams

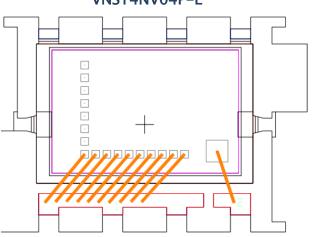

## VNS14NV04P-E

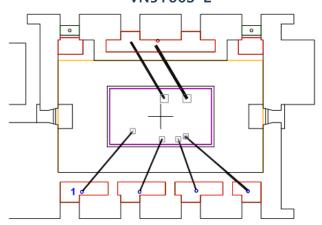

## VN5160S-E

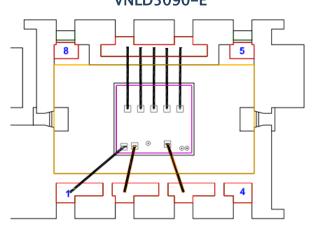

## VNLD5090-E

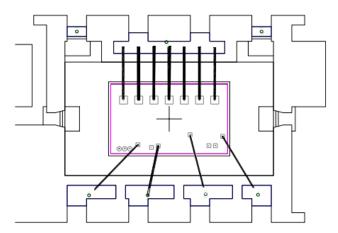

#### **VN7040AS**

RERLVIP22035 Page **13** of **20**

## 2.5 Traceability

## 2.5.1 Wafer Fab information

| Commercial Product                      | VNS3NV04DP-E | VNS14NV04P-E      | VN5160S-E   | VNLD5090-E                        | VN7040AS                               |  |  |

|-----------------------------------------|--------------|-------------------|-------------|-----------------------------------|----------------------------------------|--|--|

| Wafer fab name / location               |              | ST Singapore SG6  |             | ST Singapore SG8                  | Catania (Italy) CTM8                   |  |  |

| Wafer diameter (inches)                 |              | 6"                |             | 8                                 | "                                      |  |  |

| Silicon process technology              | VIPowei      | VIPower® M03      |             | ver® M05                          | VIPower® M0L7                          |  |  |

| Line code                               | VNS6         | VNT8              | VNJ5        | VNY9                              | XV14                                   |  |  |

| Die finishing front side                |              | SiN/POLYIMIDE     |             | Teos+PTeos+SiOn+PIX               |                                        |  |  |

| Die finishing back side                 |              | Ti-Ni-Au          |             |                                   | Ni-Au                                  |  |  |

| Die size (micron)                       | 2350 x 1720  | 2550 x 3810       | 2240 x 1270 | 1720 x 1550                       | 2500 x 1530                            |  |  |

| Metal levels/ materials/<br>thicknesses | 1 / AlSi /   | 1 / AlSi / 3.2 μm |             | 2 /Ti/TiN/TiAlCu<br>3.325 µm last | 2 /Ti/TiN/Ti/AlCu/TiN<br>3.180 µm last |  |  |

## 2.5.2 Assembly information

| Commercial Product                          | VNS3NV04DP-E                       | VNS14NV04P-E           | VN5160S-E     | VNLD5090-E  | VN7040AS      |

|---------------------------------------------|------------------------------------|------------------------|---------------|-------------|---------------|

| Assembly plant name / location              |                                    | ST Bouskoura (Morocco) |               |             |               |

| Packago description                         | SO-08 STRIP                        | SO-08 STRIP            | SO-08 STRIP   | SO-08 STRIP | SO-08 STRIP   |

| Package description                         | DUAL ISLAND                        | SINGLE ISLAND          | SINGLE ISLAND | DUAL ISLAND | SINGLE ISLAND |

| Lead frame description (material/thickness) | SO 8L 92x169 6+2 SSHD 600uOpK SpAg |                        |               |             |               |

| Die attach material                         | LOCTITE ABLESTIK QMI95072A1        |                        |               |             |               |

| Wire bonding material/diameter              | Cu D2                              |                        | Cu D1, Cu D2  | Cu D2       | Cu D1, Cu D2  |

| Molding compound material                   | SUMITOMO EME-G700KC D16mm          |                        |               |             |               |

## 2.5.3 Reliability Testing information

| Reliability laboratory location | ST Bouskoura (Morocco), ST Catania (Italy) |

|---------------------------------|--------------------------------------------|

RERLVIP22035 Page 14 of 20

## **3 TESTS RESULTS SUMMARY**

## 3.1 Lots Information

| Lot # | Product              | Diffusion Lot     | Assembly Lot | Assembly configuration Bonding Force / US Power |      |

|-------|----------------------|-------------------|--------------|-------------------------------------------------|------|

|       | VNS3NV04P-E          |                   | CZ2251K702   | N /N                                            |      |

| 1     | VNS6                 | 6205V76           | CZ2251K703   | L /L                                            |      |

| VNSO  |                      | CZ2251K701        | H / H        |                                                 |      |

|       |                      |                   |              |                                                 |      |

|       | VNS14NV04P-E         |                   | CZ2325FG01   | N /N                                            |      |

| 2     | VNST4NVU4P-E<br>VNT8 | 6209H41           | CZ2325FG03   | L /L                                            |      |

|       | VINTO                |                   | CZ2325FG02   | H / H                                           |      |

|       |                      |                   |              |                                                 |      |

|       |                      |                   | CZ2346L601   | N /N                                            |      |

| 3     |                      | VN5160S-E 6202HJF | CZ2346NFRR   | L /L                                            |      |

|       | VNJ5                 |                   | CZ2346NF01   | H / H                                           |      |

|       |                      |                   |              |                                                 |      |

|       | \/\!\\               |                   | CZ2367YB03   | N /N                                            |      |

| 4     | VNL5090S5-E          | 6205L1X           | CZ2367YB02   | L /L                                            |      |

|       | VNY9                 |                   | CZ2367YB01   | H / H                                           |      |

|       |                      |                   | 1            |                                                 |      |

|       | 5 VN7040AS<br>XV14   | V01204046         |              | CZ21705W01                                      | N /N |

| 5     |                      | 5121FKC           | CZ21805V02   | L /L                                            |      |

|       |                      | XV14              | CZ21805V01   | H / H                                           |      |

RERLVIP22035 Page **15** of **20**

## 3.2 Test results summary

Test method revision reference is the one active at the date of reliability trial execution.

TEST GROUP A - ACCELERATED ENVIRONMENT STRESS TESTS

| Test | #  | Reference                                              | AEC-Q100<br>STM Test Conditions                                                                                                                                                 | Lots | S.S. | Total | Results<br>FAIL/SS/Lots | Comments                                                             |

|------|----|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------|----------------------------------------------------------------------|

| PC   | A1 | JESD22–A113<br>J–STD–020                               | 24h bake@125°C, including 5 Temperature Cycling Ta=-40°C/+60°C  ACC MSL3 (40h@60C/60%RH)  3x Reflow simulation Peak Reflow Temp= 260°C  100 Temperature Cycling Ta=-55°C/+150°C | 5    | 405  | 2025  | 0/450/5                 | Before THB/AC/TC/HTOL/PTC                                            |

| ТНВ  | Δ) | JESD22 A101<br>JESD22 A110                             | Ta=85°C, 85%RH,<br>Duration= 1000hrs                                                                                                                                            | 5    | 90   | 450   | 0/90/5                  | 30 units / assembly lot<br>(=assembly configuration)                 |

| AC   | A3 | JESD22 A102<br>or JESD22<br>A118<br>or JESD22-<br>A101 | ENV. SEQ. Environmental Sequence TC (Ta=-55°C / +150°C for 100 cycles) + AC (Ta=121°C, Pa=2atm for 96 hours)                                                                    | 5    | 90   | 450   | 0/90/5                  | 30 units / assembly lot<br>(=assembly configuration)                 |

| TC   | A4 | JESD22 A104                                            | Ta=-55°C /+150°C<br>Duration= 1000 cycles                                                                                                                                       | 5    | 90   | 450   | 0/90/5                  | 30 units / assembly lot<br>(=assembly configuration)                 |

| PTC  | A5 | JESD22 A105                                            | Ta=-40°C /+125 °C<br>Duration=1000 cycles                                                                                                                                       | 1    | 45   | 45    | 0/45/1                  | Only for VN7040AS  15 units / assembly lot (=assembly configuration) |

| HTSL | A6 | JESD22 A103                                            | Ta= 150°C<br>Duration= 1000hrs                                                                                                                                                  | 5    | 90   | 450   | 0/90/5                  | 30 units / assembly lot<br>(=assembly configuration)                 |

TEST GROUP B - ACCELERATED LIFETIME SIMULATION TESTS

RERLVIP22035 Page 16 of 20

| Test | #  | Reference    | AEC-Q100<br>STM Test Conditions                                     | Lots | S.S. | Total | Results<br>FAIL/SS/Lots | Comments                                             |

|------|----|--------------|---------------------------------------------------------------------|------|------|-------|-------------------------|------------------------------------------------------|

| HTOL | В1 | JESD22 A108  | Bias dynamic stress ( <b>OLT</b> )<br>TJ=150°C<br>Duration= 1000hrs | 5    | 90   | 450   | 0/90/5                  | 30 units / assembly lot<br>(=assembly configuration) |

| ELFR | B2 | AEC-Q100-008 | Ta max=150°C<br>Duration=24hrs                                      | 1    | -    | -     | -                       | Not Applicable                                       |

| EDR  | В3 | AFC-0100-005 | Specific tests and conditions to be defined in case of NVM          | -    | -    | -     | -                       | Not Applicable                                       |

## TEST GROUP C - PACKAGE ASSEMBLY INTEGRITY TESTS

| Test | #  | Reference                               | AEC-Q100<br>STM Test Conditions                                       | Lots | S.S.   | Total                | Results<br>FAIL/SS/Lots            | Comments                                                      |

|------|----|-----------------------------------------|-----------------------------------------------------------------------|------|--------|----------------------|------------------------------------|---------------------------------------------------------------|

| WBS  | C1 | AEC-Q100-001<br>AEC-Q003                | Wire Bond Shear: (Cpk > 1.67)                                         | 5    | bond/m | 0<br>ninimum<br>nits | All measurement within spec limits | Performed on all assembly<br>lot (=assembly<br>configuration) |

| WBP  |    | Mil-STD-883,<br>Method 2011<br>AEC-Q003 | Wire Bond Pull: (Cpk > 1.67)                                          | 5    | bond/m | 0<br>ninimum<br>nits | All measurement within spec limits | Performed on all assembly<br>lot (=assembly<br>configuration) |

| SD   | С3 | JESD22 B102<br>ISTD-002D                | Solderability: (>95% coverage)<br>8hr steam aging prior to<br>testing | 5    | 15     | 75                   | All measurement within spec limits | Performed on all assembly<br>lot (=assembly<br>configuration) |

| PD   | C4 | IESD22 B108                             | Physical Dimensions:<br>(Cpk > 1.67)                                  | 5    | 10     | 50                   | All measurement within spec limits | Performed on all assembly<br>lot (=assembly<br>configuration) |

| SBS  | C5 | AEC-Q100-010<br>AEC-Q003                | Only for BGA package                                                  | -    | _      | _                    | -                                  | Not Applicable                                                |

| LI   | C6 | IFSD22 B105                             | Not required for Surface<br>Mount Devices                             | -    | -      | -                    | -                                  | Not Applicable                                                |

RERLVIP22035 Page **17** of **20**

## TEST GROUP D - DIE FABRICATION RELIABILITY TESTS

| Test | #  | Reference   | AEC-Q100<br>STM Test Conditions                          | Lots | S.S. | Total | Results<br>FAIL/SS/Lots | Comments       |

|------|----|-------------|----------------------------------------------------------|------|------|-------|-------------------------|----------------|

| EM   | D1 |             | Data, test method and criteria<br>available upon request | -    | -    | -     | -                       |                |

| TDDB | D2 |             | Data, test method and criteria<br>available upon request | -    | -    | -     | -                       |                |

| HCI  | D3 |             | Data, test method and criteria<br>available upon request | -    | -    | -     | -                       | Not Applicable |

| NBTI | D4 | II EXI 1911 | Data, test method and criteria<br>available upon request | -    | -    | -     | -                       |                |

| SM   | D5 |             | Data, test method and criteria<br>available upon request | -    | -    | _     | -                       |                |

## GROUP E - ELECTRICAL VERIFICATION

| Test | #   | Reference                        | AEC-Q100<br>STM Test Conditions                          | Lots | S.S. | Total | Results<br>FAIL/SS/Lots        | Comments                            |

|------|-----|----------------------------------|----------------------------------------------------------|------|------|-------|--------------------------------|-------------------------------------|

| TEST | E1  | User/Supplier<br>Specification   | Pre and Post Stress<br>Electrical Test                   | All  | All  | All   | Passed                         | All parametric and functional tests |

| НВМ  | E2  | AEC-Q100-002                     | Target: ±2kV                                             | -    | -    | -     | -                              | Not Applicable                      |

| CDM  | E3  | AEC-Q100-011                     | Target:<br>±750V on corner pins                          | _    | -    | _     | -                              | Not Applicable                      |

| LU   | E4  | AEC-Q100-004                     | Current Injection<br>Class II – Level A (+/-             | -    | -    | -     | -                              | Not Applicable                      |

| ED   | F 5 | AEC-Q100-009<br>AEC-Q003         | Electrical Distributions: (Test<br>@ Rm/Hot/Cold) (where | 5    | 30   | 150   | All measurement<br>within spec |                                     |

| ЕМС  | E9  | SAE J1752/3                      | Electromagnetic<br>Compatibility (Radiated<br>Emissions) | -    | -    | -     | -                              | Not Applicable                      |

| SC   | E10 | AEC Q100-012                     | Short Circuit Characterization                           | -    | -    | -     | -                              | Not Applicable                      |

| SER  |     | JESD89–1<br>JESD89–2<br>JESD89–3 | Applicable to devices with memory                        | -    | -    | -     | -                              | Not Applicable                      |

| LF   | E12 | AEC-Q005                         | Lead (Pb) Free: (see AEC-<br>Q005)                       | -    | -    | -     | -                              | Not Applicable                      |

RERLVIP22035 Page **18** of **20**

#### **TEST GROUP F - DEFECT SCREENING TESTS**

| Test | #  | Reference | AEC-Q100<br>STM Test Conditions                   | Lots                                                                                           | S.S. | Total | Results<br>FAIL/SS/Lots | Comments |

|------|----|-----------|---------------------------------------------------|------------------------------------------------------------------------------------------------|------|-------|-------------------------|----------|

| PAT  | F1 | AFC-0001  | Process Average Testing: (see<br>AEC-Q001)        | Not performed on qualification lots. It will be implemented starting from first production lot |      |       |                         |          |

| SBA  | F2 | AFC-0002  | Statistical Bin/Yield Analysis:<br>(see AEC-Q002) |                                                                                                |      |       |                         |          |

#### TEST GROUP G - CAVITY PACKAGE INTEGRITY TESTS

| Test | #  | Reference                  | AEC-Q100<br>STM Test Conditions | Lots                                             | S.S. | Total | Results<br>FAIL/SS/Lots | Comments |  |  |

|------|----|----------------------------|---------------------------------|--------------------------------------------------|------|-------|-------------------------|----------|--|--|

| MS   | G1 | JESD22 B104                | Mechanical Shock                |                                                  |      |       |                         |          |  |  |

| VFV  | G2 | JESD22 B103                | Variable Frequency Vibration    |                                                  |      |       |                         |          |  |  |

| CA   | G3 | MIL-STD-883<br>Method 2001 | Constant Acceleration           |                                                  |      |       |                         |          |  |  |

| GFL  | G4 | MIL-STD-883<br>Method 1014 | Gross and Fine Leak             | Not Applicable: not for plastic packaged devices |      |       |                         |          |  |  |

| DROP | G5 |                            | Drop Test, Package Drop         |                                                  |      |       |                         |          |  |  |

| LT   | G6 | MIL-STD-883<br>Method 2004 | Lid Torque                      |                                                  |      |       |                         |          |  |  |

| DS   | G7 | MIL-STD-883<br>Method 2019 | Die Shear                       |                                                  |      |       |                         |          |  |  |

| IWV  | G8 | MIL-STD-883<br>Method 1018 | Internal Water Vapor            |                                                  |      |       |                         |          |  |  |

RERLVIP22035 Page **19** of **20**

#### **TERMS OF USE**

BY ACCEPTING THIS REPORT, YOU AGREE TO THE FOLLOWING TERMS OF USE:

This Reliability Evaluation Report (the "Report") and all information contained herein is the property of STMicroelectronics ("ST") and is provided solely for the purpose of obtaining general information relating to an ST product. Accordingly, you hereby agree to make use of this Report solely for the purpose of obtaining general information relating to the ST product. You further acknowledge and agree that this Report may not be used in or in connection with any legal or administrative proceeding in any court, arbitration, agency, commission or other tribunal or in connection with any action, cause of action, litigation, claim, allegation, demand or dispute of any kind. You further acknowledge and agree that this Report shall not be construed as an admission, acknowledgement or evidence of any kind, including, without limitation, as to the liability, fault or responsibility whatsoever of ST or any of its affiliates, or as to the accuracy or validity of the information contained herein, or concerning any alleged product issue, failure, or defect. ST does not promise that this Report is accurate or error free and specifically disclaims all warranties, express or implied, as to the accuracy of the information contained herein. Accordingly, you agree that in no event will ST or its affiliates be liable to you for any direct, indirect, consequential, exemplary, incidental, punitive, or other damages, including lost profits, arising from or relating to your reliance upon or use of this Report. You further acknowledge and agree that the use of this Report in violation of these Terms of Use would cause immediate and irreparable harm to ST which could not adequately be remedied by damages. You therefore agree that injunctive relief is an appropriate remedy to enforce these Terms of Use.

Disclosure of this document to any non-authorized party must be previously authorized by ST only under the provision of a proper confidentiality contractual arrangement executed between ST and you and must be treated as strictly confidential.

At all times you will comply with the following security rules:

- · Do not copy or reproduce all or part of this document

- · Keep this document locked away

- · Further copies can be provided on a "need to know basis", Please contact your local ST Sales Office or document writer

Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement, including, without limitation, the warranty provisions thereunder.

In that respect please note that ST products are not designed for use in some specific applications or environments described in above mentioned terms and conditions.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

Information furnished is believed to be accurate and reliable. However, ST assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license, express or implied, to any intellectual property right is granted by ST herein.

ST and ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior version of this document.

©2022 STMicroelectronics - All rights reserved

RERLVIP22035 Page **20** of **20**